Technical Briefs

Marvels of Microelectronic Technology: The 1T–1C Dynamic Random Access Memory, from a Groundbreaking Idea to a Business Benchmark

by Simon Deleonibus, Past Chief Scientist, CEA, LETI

In this issue, we report on one of the flagship Marvels of Microelectronic Technology, which has marked the history of microelectronics in the past 50 years: the 1 Transistor –1 Capacitor Dynamic Random Access Memory (1T1C DRAM). DRAMs have driven and accompanied Moore’s Law through Metal Oxide Semiconductor Field Effect Transistor (MOSFET) integrated circuit scaling. They have been and still are a benchmark for the microelectronics industry: they continue to share their leadership with advanced microprocessors, SOCs and nonvolatile memories. DRAM fostered technological progress that was necessary to introduce new materials and revise process integration. In this article, R.H. Dennard, H. Sunami, M. Koyanagi and K. Itoh (Figure 1) accepted to remind us the pioneering times when 1T1C DRAM came out of its cradle.

Figure 1 From left to right: (Standing) Hideo Sunami and Mitsumasa Koyanagi (Sitting) Kiyoo Itoh and Robert Dennard at the 2006 IEEE Award Ceremony. Itoh, Sunami, and Koyanagi were honored with the 2006 IEEE Jun-Ichi Nishizawa Medal. (Front cover of IEEE SSC Newsletter, Winter 2008, vol. 13, n°.1)

DRAM Invention and First Developments

The groundbreaking ideas proposed by Robert Dennard, IEEE Fellow, IBM Fellow, to push microelectronics progress thanks to the 1T1C DRAM and MOSFET integrated circuit scaling have already been widely commented and many times awarded. The circumstances giving birth to the idea of MOSFET scaling were reported in the IEEE EDS Newsletter July 2019 issue. In this issue (October 2019), we will report the advent of 1T1C DRAM. Robert Dennard kindly accepted to remind us a few important facts. Some of them were also reported at his 2013 Kyoto Prize Award ceremony as well as in journals/magazines papers [1], [2].

In the time period of Dennard’s invention (mid-1960s), IBM mainframe computers were equipped with a maximum of 1 MB magnetic-core memory capacity. The access time was in the range of 1–2 microseconds, and power dissipation was about 40 kW. Those features are orders of magnitude larger than the ones we are used to on our today’s handheld mobile phones! In 1971, the first semiconductor memory equipped IBM mainframe computers were based on 128 bit/chip bipolar design [2]. The six transistor (6T) memory cell (2 cross coupled flip flops and 2 bitlines access transistors) was the standard benchmark reference [3]. To compensate the lack of performance of 6T MOSFET arrays, Pleshko and Terman proposed to interface them with bipolar support circuits in order to drive large interconnect loads with low impedance devices [4]. n-MOSFET design started to be convincing by its potential lower cost and scalability, coming together with a speed increase and reduced power consumption, which narrowed the gap with bipolar Figures [5].”

Dennard was struck by an unexpected fact, where he states: “One day in late 1966 an important event in my life occurred. During the day I attended a large IBM Research conference where various projects were presented. … I was very impressed by a description of a proposed thin-film magnetic memory, which was projecting hundreds of thousands of bits in a 25 cm wide memory board… they had a very simple memory cell, just a small square of magnetic material at the intersection of two etched copper lines. I was inspired to find something that simple for the technology we were developing.” [1], [2]

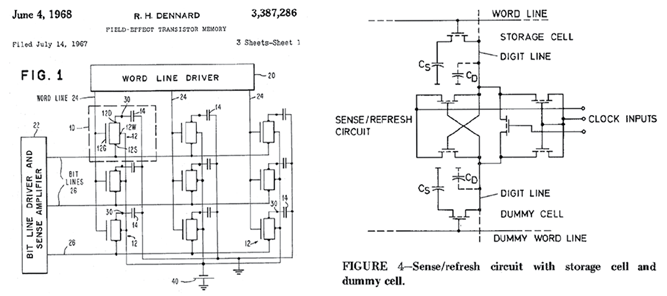

Such a simple idea has been so powerful in the long term and is still a source of inspiration nowadays to those who build cross bar arrays or are ever looking for the Universal Memory. “I found that an MOS transistor in series with each capacitor could be used as a switch to connect the capacitor to a data line briefly to charge or discharge it to write a data bit, represented by a positive voltage level, +V, or a zero voltage level on the bit line. The transistor is turned on and off by a control signal on a word line which allows selecting a given capacitor from many others for receiving the data on that bit line.” [1], [2] The basic idea of 1T1C DRAM was born that same day in late 1966. Dennard restlessly kept on working for several weeks on various configurations. He finally realized that the stored charge could be written and read through the same nonlinear device which is the access transistor, that would create a small signal on the bit line: “The cell had been reduced to a single transistor and a capacitor at the intersection of two access lines [1], [6]. I was satisfied that this was as close to my goal as possible, and offered a great reduction in complexity compared to the six-transistor memory cell.”(Figure 2 Left)

Figure 2 (Left) Detail from R.H. Dennard’s 1st Patent of 1T1C DRAM [6]; (Right) Open Bitline 1T1C DRAM array architecture by K.U. Stein et al. presented at 1972 IEEE ISSCC [11]. The sense-and-refresh circuit is shared by 2 bitlines both connected to a large number of DRAM storage and dummy memory cells (first pair only represented) through two latch nodes

Nevertheless, MOSFET technology needed to prove its capability because the mainly used p-channels transistor speed was lower than for the bipolar competitor. Moreover, MOSFETs’ characteristics, based on interface inversion, were still not well controlled. In that context, Intel realized the first silicon gate 3 p-channel transistor DRAM in 1970 [7]. The first proposal of 2 kbits “One device RAM chip” design, based on MOSFET technology, was published in 1971 [8]. 4 kbit chips became commercially available in the mid 1970s.

Besides the technology, further development consisted in layout optimization to pack up as much as possible the bit cell, possibly including self-aligned contacts and two poly layers, to realize both a transistor gate and a capacitance plate [9]. At the chip level, innovations were guided by the necessity to match bitlines and wordlines pitches, including the row and column decoders layout, with the bit cell arrays without sacrificing the performance and noise Figures [9]. The small signals delivered by the bitcell and the necessity to restore them requested innovations in the design of the sense amplifiers [2]. Dennard reminds how critical it was to make DRAM products design manufacturable from the first idea of latch based sense amplifier in 1970 [10] and the implementation of the Open Bitline architecture using a cross-coupled differential sense amplifier based on a combination of each bitcell with a dummy cell, first presented at the 1972 ISSCC [11] (Figure 2 Right), refined in its “double cross coupled” version in IBM’s 64 kBit DRAM in 1977 [12]. However, the solution to noise problems, potentially introduced by imbalances in the arrays, was brought by the Folded Bitline architecture invented by Itoh [13] in 1974 (see more hereunder “Folded Bitline and revised Open Bitline architectures” section). At this early stage of development, the necessity to introduce redundancy in order to maximize production yield appeared and was reported by IBM and Bell Laboratories [14], [15].

In the early days, Dennard’s approach received also criticism, including internally at IBM, despite the fact that the architecture was considered as the simplest for a memory cell. As an example, we report a comment on 1T1C DRAM drawbacks “The cell has a number of drawbacks… the readout is destructive, the stored charge distributes between the cell and bit line capacitances and the writing speed is limited by the information storage capacitor which must be made large enough to yield a reasonable sense charge” [5]. However, Dennard explains that such a specific situation can be managed: “A distinctive characteristic of this memory cell is that a small leakage current from this n-doped region to the p-type silicon substrate discharges the capacitor in a fraction of a second. This gives rise to the name “dynamic” since the data is only stored temporarily. To preserve the data it must be refreshed by reading it out and writing it back into each cell at certain intervals. Fortunately, the speed of this memory scheme allows more than a hundred million read or write operations per second and only a small percentage of these are needed for refreshing the data. Thus, this scheme became known as dynamic RAM, and commonly called DRAM.” [1]

Once the 1T1C concept was proven, competition started raging to scale down the memory devices driven by performance and density increase. At Hitachi, another main frame computer company, two concepts came out almost concomitantly, driven by two talented imaginative engineers, IEEE Fellows and Professors Hideo Sunami and Mitsumasa Koyanagi, as original solutions to respond to the scaling challenge. One was using capacitors embedded into trenches etched in the substrate and the second one stacked a capacitor on top of the addressing (write/refresh, sense/erase,) devices. These approaches were among the first attempts to exploit the 3rd-Dimension to improve microelectronics circuit density and were going to become benchmark circuits for technology scaling, but their inventors probably were not conscious of it, at the time.

Trench Capacitor DRAM

Hideo Sunami proposed the trench capacitor approach. He was inspired by a combination of Dennard’s 1T1C approach, his background on electronic components engineering and his youth passion for radio engineering. He entered Tohoku University in 1963 and joined Hitachi Central Research Laboratory (CRL) in 1969 after his graduation from Prof. Junichi Nishizawa’s laboratory in 1969.

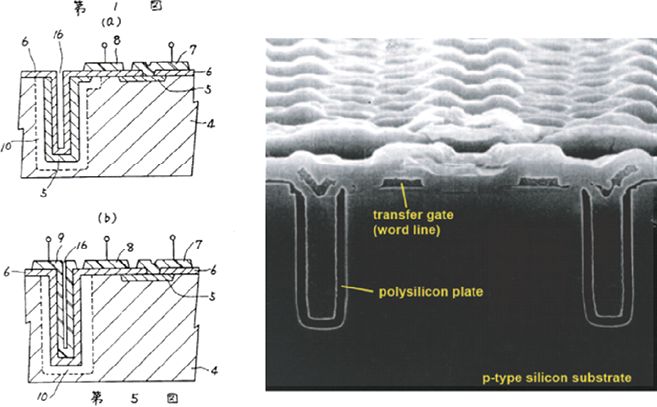

Hideo Sunami was very much involved in CCD research at Hitachi and that naturally led him to be interested in the DRAM because CCD were very demanding in terms of silicon engineering and more precisely gettering, doping and materials purity control. He proposed to make the capacitor of the 1T1C DRAM by etching a trench capacitor into silicon. Sunami thought that by adjusting the trench depth the capacitance value could be increased without increasing the capacitor footprint [16] (Figure 3 Left). Sunami told us: “At an early stage of my junior-high school age I fell in love with two hobbies. One was collecting butterflies and the other was hand making of short-wave radio receivers and transmitters. Then I have made myself to be very familiar to electronic components such as vacuum tubes, transistors, resistors, capacitors, etc. by the time I entered Tohoku University in 1963.”

Figure 3 (Left) Trench Capacitor DRAM patent H. Sunami and S. Nishimatsu, Japanese patent application, Tokugansho 50-53883, 1975 [16]; (Right) SEM cross section of first 1-Mbit Trench Capacitor cell DRAM, presented at 1982 IEDM by Sunami et al. [18]

Hitachi CRL offered him a leave opportunity at Stanford University. His imagination was struck by marvels achieved in a completely different area while he attended a conference: “In the conference I was awfully shocked by some presentation where truly vertical trench of aspect ratio of almost 5 was formed on (110)-oriented silicon surface. In those days, truly vertical trench could not be formed on silicon surface but spherical crater-like hollow was formed even by using plasma etching.” He knew from his experience on CCD that surface characterization was a major tool to master the integrity and reliability of silicon devices.

Sunami continues: “On the other hand, I was hearing that one-device and one-capacitor DRAM cell had been recently invented. Despite the on-going research on surface characterization at Stanford, I got an inspiration of a first trench capacitor cell concept based on a combination of that DRAM cell and a cylindrical trimmer condenser used in radio-frequency transmitter. I requested my department boss at CRL to send me abroad a patent application form. His answer was negative. He told me: “You should concentrate on on-going research.” Therefore, the first trench-capacitor cell patent was applied in 1975, several months after I left Stanford. Since the patent was not classified to be excellent, it was not applied to US!”

In the late 1970s and 1980s, Hitachi became one of the major actors on the DRAM business by first introducing Trench capacitor DRAM. Hitachi’s 1-Mb DRAM was first presented at 1984, ISSCC [17] featuring a Corrugated Cell Structure that was first reported at 1982 IEDM [18] (Figure 3 Right) and received the IEEE Paul Rappaport Award in 1984 [19].

Stacked Capacitor DRAM Cell

Another challenging approach to the scaling of DRAMs was the 1T1C cell using a so called “Stacked Capacitor.” While the storage capacitance decreases by following their linear scaling, the number of stored charges decreases. The stored charge can thus incur severe variations. Mitsumasa Koyanagi points out: “The number of signal charges stored in the storage capacitor has to be maintained at almost a constant, or can be only slightly reduced, as the memory cell size is scaled down. However, MOS capacitor value—and hence the amount of signal charges—is significantly reduced as the memory cell size is reduced, even if the capacitor oxide thickness is scaled-down. Therefore, I forecasted in 1975 that the 1-T cell with a two-dimensional (2D) structure using a planar MOS capacitor eventually would encounter a scaling-down limitation because it was not possible to reduce the MOS capacitor area according to the scaling theory.” [20] The second reason to find an alternative was to reduce the influence of minority carriers generated in the silicon substrate on the storage node charges, degrading thus retention time and soft error immunity.

Using a vertical capacitor (exploitation of the 3rd-dimension) would give more flexibility to fix the capacitance value. If the vertical capacitor is located far from the silicon substrate, then the degradation of retention and soft errors immunity by the minority carriers is dramatically reduced.

“An inversion layer capacitance and a depletion layer capacitance are connected with the gate oxide capacitance in series in the MOS capacitor. The charges in the inversion layer and the depletion layer are easily affected by the minority carriers, which are thermally or optically generated or generated by the irradiation of energetic particles in a silicon substrate.”

Koyanagi had a good knowledge of MOS interface physics. “In my Ph.D. research during 1971–1974 [3], I had commented on the silicon surface and the inversion layer in MOS structures. To evaluate the electrical properties of the interface states and the inversion layer, I myself built an impedance analyzer with the frequency range of 0.01 Hz to 100 MHz. I examined various kinds of capacitors, including high-k (high dielectric constant) capacitors as a reference capacitor of this impedance analyzer. Eventually, I made a vacuum capacitor for a reference capacitor in which fin-type capacitor electrodes were encapsulated in a vacuum container.”

Koyanagi also used a Ta2O5 film as a capacitor insulator for the first time [21]. Ta2O5 has a dielectric constant five or six times larger than that of SiO2. Therefore, the storage capacitance can greatly be increased, although the leakage current is larger than for SiO2 or Si3N4 (for the same thickness) because of a lower bandgap value.

Koyanagi proposed the Capacitor Over Bitline (COB) concept which laid out the capacitor structure on top of the access transistor [21], [22], [23] (Figure 4). Many ways have been explored to increase the capacitance value per unit area by playing with the actual capacitance area spread in 3D either by wrapping multiple electrodes (Fin type capacitors , 1st publication by Fujitsu in 1988 [24]), increasing the plate electrode area with large hemispherical grains polysilicon(1st publication by NEC in 1990 [25]), or a cylindrical capacitor (1st publication in 1989 by Mitsubishi [26]) which have been extended to Multigigabit DRAMs till nowadays.

Figure 4 (Left ) Capacitor over Bitline Basic principle of stacked capacitor cell DRAM [22]; (Middle) 3 µm NMOS Stacked capacitor DRAM presented by M. Koyanagi et al. at IEDM 1978 [21]; (Right) Schematic cross-section of Capacitor Over Bitline [20]

The concept of the COB-type stacked capacitor cell—that various kinds of materials can be stacked on the switching transistor using a lower temperature process—has been carried on in new memories with a three-dimensional structure such as Fe-RAM (Ferroelectric RAM), P-RAM (Phase Change RAM), R-RAM (Resistive RAM) and M-RAM (Magnetic RAM). [20]

Further on Koyanagi spent much of his energy on the generalization of 3D stacking. His work with his team at Tohoku University is recognized as a reference in the packaging and 3D community. By intensively using wafer bonding and Through Silicon Vias (TSV), he has been instrumental in creating a way to give a new breath to Moore’s law. He did that not only to increase DRAM capacity but also to cointegrate heterogeneously different types of circuits [27].

Soft Errors and the “DRAM Midlife Crisis”

Once the DRAM circuits complexity and production volume increased, stochastic and statistical effects started to appear such as Soft Errors. In 1979, two research groups at Intel [28] and Bell Laboratories [29] revealed that 16kbit DRAMs could suffer from transient error due to bombardment by alpha-particles and subsequent excess minority carrier generation in the substrate. Dennard points out: “The alpha particles were identified as coming from radioactive impurities in the materials of the hermetically-sealed packages…an analysis of the possible soft-error rate due to cosmic rays showed that this source could be significant. Personally, I felt very responsible because of my early role with dynamic RAM’s and because I failed to anticipate the problem.” [1] A good understanding required building a model based on a Monte Carlo approach developed by G Sai-Halasz. A solution based on a self-aligned buried n-grid to protect against radiation-induced charge collection was proposed [30] (Figure 5 Left): “It was shown that error rates would rise in response to scaling to smaller dimensions, but that design changes including error-correction techniques would contain the problem. The midlife crisis was over.”

Figure 5 (Left) Self aligned buried n-grid protection for soft error immunity, as proposed by Wordemann et al. [30]; (Right) Dependence of Soft Error Rate on 16 kDRAM cycle time. Comparison of Stacked Capacitor Cell and unprotected Planar Capacitor Cell [20]

In our exchanges, Dennard further commented: “IBM was also careful to replace radioactive lead and other sources of alpha-particle emissions in order to limit soft-error rates (SER). IBM chose trenches to avoid disrupting our back end of line (BEOL) process with a tall stacked capacitor. The designers wanted a big memory-cell capacitor to support large arrays (long bit lines) and we knew how to etch really deep trenches.”

Within Hitachi, the concern on SER, besides the caution taken on packaging, led to make drastic choices on the architecture. The different approaches of Trench DRAM and Stacked capacitor (STC) were shown to behave quite differently with respect to the soft errors. Sunami comments “Hitachi was one of the biggest main frame makers in the world at that time, and was as much concerned like IBM, the huge giant. The computer division of Hitachi became very nervous to degraded SER of which home-made DRAM provided.” He considers that DRAM in consumer equipment market did not require main-frame level SER. Consequently, many manufacturers such as NEC, Toshiba, IBM, TI, Siemens shipped 1-Mbit DRAM integrating trench capacitors. “Some of them applied modified trench capacitors having improved SER.” The idea was based on the collection of minority carriers through a highly conductive buried electrode. Examples such as the use of self-aligned buried grids [30], p+ substrate or n+ sheath plates under the storage capacitor have been used [31], [32], [33], as well, to control cell to cell leakage current.

Koyanagi showed to the DRAM community in Japan the results that a soft error rate could be dramatically reduced by almost three orders of magnitude by employing a Stacked Capacitor Cell as compared to a planar capacitor cell. This very important result was mentioned in his IEEE TED paper in 1980 [34]. Koyanagi comments: “My boss in Hitachi at that time cut the Figure of soft error characteristics from the 1980 TED paper. He said that data of STC soft error was very important internally in Hitachi and hence data indicating the superior immunity to soft error of STC should be confidential for outside.” Koyanagi obtained permission for publication on the evidence of the superiority of STC on soft error immunity only in a Japanese paper [35]. The Figure demonstrating such a superiority appeared in IEEE SSCS News in 2008 [20] (Figure 5 Right). Koyanagi concludes: “Today, the three major DRAM companies are Samsung, Hynix and Micron. These three DRAM companies have been using the Stacked Capacitor Cell from 4 Mbit DRAM to 8 Gbit DRAM and maybe 16 Gbit DRAM.”

Folded Bitline and Revised Open Bitline Architectures

Another benchmark innovation for DRAM success, that had become an industry standard from the 1980s to the mid-2000s, is the invention of the Folded Bitline (Folded BL) arrangement at the end of 1974 by IEEE Fellow Kiyoo Itoh of Hitachi CRL [13]. The first demonstration was made by a presentation of a 64-kb DRAM at ISSCC in Feb. 1980 [36].

The Folded BL uses a pair of balanced BLs running close to one another and are parallel on the same conductor, equalizing and thus cancelling noise voltages coupled to the pair, caused by voltage bounces in an array, with the differential amplifier [37] (Figure 6) . Moreover, a metal BL reduced soft-error noise caused by diffused-BL structures of the Open BL. Although in principle the Open BL realizes a smaller cell size of 6F2 (F is feature size) than the Folded BL (8F2), the much larger cell compensates the noise voltages with a larger signal voltage. Itoh comments: “Unfortunately, a simple single metal-layer 5-µm process available at that time could not suppress the noise voltages sufficiently. Consequently, the 64-kb DRAM enabled stable operations despite a drastic reduction of the operation voltage VDD to a TTL-compatible 5 V from 12 V for the 16-kb DRAM…In the cradle of DRAM, no one knew solutions for stable operations under array noise and soft errors and thus at the beginning I could not convince top managers on the importance of the innovation.” Since that time until the mid-2000s, the Folded-BL was adopted for nearly all DRAM chips produced. In 2002, however, based on in-depth analysis of array noise, Itoh’s team [38] revealed the possible revival of the open-BL with 6F2, if an advanced vertical capacitor cell for a larger cell signal voltage and a three-level metal layer process for reduced voltage bounces were used. Triggered by the 2002 JSSC paper [38], major DRAM players such as Samsung, SK Hynix and Micron have gradually changed the cell to the 6F2 Open BL, starting with 512-Mb DRAMs in 2005 [39], reaching nowadays 10-nm-class 16-Gb DRAMs [40]. Stacked modules with 8 single-16-Gb-DRAM chips [41] contribute to high density servers and mobile applications. Itoh underlines: “The addition of an on-chip voltage down-converter to protect internal miniaturized devices [42] and reduction circuits of the ever-larger subthreshold-leakage current [43], are also key contributors to DRAM success.”

Figure 6 Comparisons of [37]: (a) Open Bitline arrangement and (b) Folded-Bitline arrangement. SA: Sense amplifier; Y; Column select-line; I/O: Common data-in- and data-out-lines-see also [13]

The simplicity of Dennard’s 1T-1C DRAM principle has kept it unbeaten by any other solution and certainly qualifies it a Marvel of Microelectronic Technologies. A lot of technical progress has been achieved worldwide, since its invention, year after year: Dennard, Sunami, Koyanagi and Itoh are certainly key persons who made it happen. Future prospect to reach a smallest footprint of 4F2 have already been highlighted, thanks to a vertically stacked access transistor and a high aspect ratio capacitor based cell [44], featuring a revised Open BL architecture.

References

[1] R.H. Dennard, “Reflections on Creativity in My Microelectronics Career,” 2013 Kyoto Prize Lecture, 18 pages Available at: https://www.kyotoprize.org/wp/wp-content/uploads/2016/02/29kA_lct_EN.pdf

[2] R.H Dennard, “EvolutionFET Dynamic RAM—A Personal View,” IEEE Trans on Electron Devices, vol. ED-31, n¨11, pp. 1549–1555, 1984 and RH Dennard, “Revisiting Evolution of the MOSFET Dynamic RAM—A Personal View,” IEEE SSCS NEWS, Winter 2008, p. 10, 2008.

[3] J.D. Schmidt, “Integrated MOS random access memory,” Solid State Design, p.21, Jan. 1965.

[4]. P. Pleshko and L.M. Terman, “An investigation of the potential of MOS transistors memories,” IEEE Trans. On Electron. Computer, vol EC-15, Aug 1966, pp. 423–427.

[5] L.M. Terman, “MOSFET Memory Circuits,” Proc. IEEE, vol. 59, pp. 1044–1058, July 1971.

[6] R.H. Dennard, “Field Effect Transistor Memory,” US Patent 3 387 286, June 4, 1968.

[7] W.M. Regitz and J.Karp, “A three transistor cell 1024 bits, 500ns MOS RAM,” ISSCC Tech. Dig. p.42, Feb 1970.

[8] L.Cohen, R. Green, K.Smith, and J.L. Seely, “Single-transistor cell makes room for more memory on a MOS chip,” Electronics, p. 69, Aug. 2, 1971.

[9] V.Leo Rideout, “One-Device Cells for Dynamic Random-Access Memories: A Tutorial,” IEEE Transactions on Electron Devices, Vol. ED-26, No. 6, June 1979.

[10] D.L. Chritchlow, “Sense Amplifier for IGFET Memory,” IBM Tech Discl. Bull., vol. 13, n°6, p. 1720, 1970.

[11] K.U. Stein, A. Sihling, E. Doering, “Storage Array and Sense/Refresh Circuit for Single-Transistor Memory Cells,” ISSCC Dig. Tech. Papers. pp. 56–57, Feb. 1972.

[12] Heller, L.G. and Spampinato, D.P., “Cross-Coupled Charge Transfer Sense Amplifier Circuits,” U.S. Patent 4,039,861; Aug. 2, 1977, and L.G. Heller, “Cross-Coupled Charge-Transfer Sense Amplifier,” ISSCC Tech Digest, pp. 20, 1979.

[13] K. Itoh, Jap Patent-1146400, filed Dec. 25, 1974 and US Patent-4044340, Dec. 29, 1975.

[14] Schuster, S.E., “Multiple Word/Bit Line Redundancy for Semiconductor Memories,” IEEE J. Solid-State Circuits, 92-13, pp. 698–703, 1978.

[15] R. Cenker , D. Clemons , W. Huber et al. , “A fault-tolerant 64K dynamic RAM,“ ISSCC Tech Digest , p. 150, 1979.

[16]. H. Sunami and S. Nishimatsu, Japanese patent application, Tokugansho 50–53883, 1975.

[17] K. Itoh, R. Hori, J. Etoh et al, “An Experimental 1Mbit DRAM with On-Chip Voltage Limiter,” Technical Digest of IEEE Internat. Solid-State Circuits Conf., pp. 282-283, San Francisco, Feb. 22–24, 1984.

[18] H. Sunami, T. Kure, N. Hashimoto et al., “A CORRUGATED FOR CAPACITOR MEGABIT DYNAMIC MOS MEMORIES CELL (CCC),” Dig. of Tech. Abstracts IEDM 1982, pp. 806–808.

[19] H. Sunami, T. Kure, N.Hashimoto et al., “A Corrugated Capacitor Cell (CCC),” IEEE Trans. Electron Devices, Vol. ED-31, No. 6, pp. 746–753, 1984 .

[20] Mitsumasa Koyanagi, “The Stacked Capacitor DRAM Cell and Three-Dimensional Memory,” IEEE SSCS News, pp. 37–41, Winter 2008.

[21] M. Koyanagi, H. Sunami, N. Hashimoto and M. Ashikawa, “Novel High Density, Stacked Capacitor MOS RAM,” Ext. Abs. of the 10th Conference on Solid State Devices, 1978.

[22] M. Koyanagi and K. Sato, Japanese patent application, Tokugansho 51-78967, 1976. and M. Koyanagi and K. Sato, USP-4151607, Jan. 5, 1977.

[23] M. Koyanagi, H. Sunami, N. Hashimoto and M. Ashikawa, “Novel High Density, Staked Capacitor MOS RAM,” IEDM Tech. Dig., pp. 348–351, Dec. 1978.

[24] T. Ema; S. Kawanago, T. Nishi et al., “3-dimensional stacked capacitor cell for 16 M and 64 M DRAMS,“ IEDM, pp. 592–595, 1988.

[25] M. Sakao, N. Kasai, T. Ishijima et al. “A CAPACITOR-OVER-BIT-LINE (COB) CELL WITH A HEMISPHERICAL-GRAIN STORAGE NODE FOR 64Mb DRAMS,” IEDM, pp. 655–658, 1990.

[26] W. Wakamiya, Y. Tanaka, H. Kimura et al., “Novel Stacked Capacitor Cell for 64Mb DRAM,” Symposium on VLSI Technology Dig. Tech. Papers, pp. 69–70, 1989.

[27] T. Fukushima, Y. Yamada, H. Kikuchi, and M. Koyanagi, “New Three-Dimensional Integration Technology Using Self-Assembly Technique,” IEDM Tech. Dig., pp. 359–362, Dec. 2005.

[28] T.C. May and M.H. Woods, “Alpha Particles Induced Soft Errors in Dynamic Memories,” IEEE Trans. On Electron Devices, vol. ED-26, n°1, pp. 2–9, 1979.

[29] D.S. Yaney, J.T. Nelson, L.L.Vanskike, “Alpha-Particle Tracks in Silicon and their Effects on Dynamic MOS RAM Reliability,” IEEE Trans. On Electron Devices, vol. ED-26, n°1, pp.10–16, 1979.

[30] M.R. Wordeman R.H. Dennard G.A. Sai-Halasz, “A Buried n-grid for Protection Against Radiation-Induced Charge Collection in Electronic Circuits,” IEDM Digest Tech. Papers, pp. 40–43, 1981.

[31] N. Lu, P. Cottrell, W. Craig et al., “THE SPT CELL—A NEW SUBSTRATE-PLATE TRENCH CELL FOR DRAMS,” IEDM Tech Digest, pp. 771–772, 1985.

[32] Sunami H., Kure T., Kawamoto Y. and Miyao M., Semiconductor Memory, Japanese patent application: Tokuhansho 57-192478(1982); Semiconductor memory, US Patent 4,901,128.

[33] Toru Kaga, Yoshinobu Nakagome, Hideo Sunami et al., “Half- Vcc Sheath-Plate Capacitor DRAM Cell with Self-Aligned Buried Plate Wiring,” IEEE Trans. on Electron Devices , ED-35, n°8, pp. 1257–1263, 1988.

[34] Mitsumasa Koyanagi, Yoshio Sakai, Masamichi Ishihara et al., “A 5-V Only 16-kbit Stacked-Capacitor MOS RAM,” IEEE Transactions on Electron Devices;, Vol. ED-27, n°8, August 1980, pp. 1596–1601.

[35] M. Koyanagi, Y. Sakai, M. Ishihara et al. “16-kbit Stacked Capacitor MOS RAM,” IEICE Technical Report (Japanese), SSD80–30, 1980.

[36] K. Itoh, R. Hori, H. Masuda et al., “A single 5V 64K dynamic RAM,” ISSCC Dig. Tech. Papers, pp. 228–229, Feb. 1980.

[37] Kiyoo Itoh, “The History of DRAM Circuit Designs—At the Forefront of DRAM Development,” IEEE SSCS News, pp. 27–31, Winter 2008

[38] T. Sekiguchi, K. Itoh, T. Takahashi et al., “A low-impedance open-bitline array for multigigabit DRAM,” JSSC, vol. 37, pp. 487–498, Apr. 2002.

[39] Geoff MacGillivray “Process vs. Density in DRAM,” EE Times, 07.04.05.

[40] Seokbo Shim, Sungho Kim, Jooyoung Bae et al., “A 16Gb 1.2V 3.2Gb/s/pin DDR4 SDRAM with Improved Power Distribution and Repair Strategy,” ISSCC Dig. Tech. Paper, pp. 212–213, Feb. 2018.

[41] Seongju Lee, Byungdeuk Jeon, Kyeongpil Kang et al., “A 512GB 1.1V Managed DRAM Solution with 16GB ODP and Media Controller,” ISSCC Dig. Tech. Paper, pp. 384–385, Feb. 2019.

[42] M. Horiguchi, M. Aoki, J. Etoh et al., “Dual-Regulator dual-Decoding-Trigger DRM Voltage Limiter for Burn-In Test,” JSSC, vol. 26, no.11, pp. 1544–1549, Nov. 1991.

[43] M. Horiguchi, T. Sakata, and K. Itoh, “Switched-Source-Impedance CMOS Circuit For Low Standby Subthreshold Current Giga-Scale LSI’s,” IEEE JSSC, vol. 28,n11, pp. 1131–1135, Nov. 1993.

[44] Ki-Whan Song, Jin-Young Kim, Huijung Kim et al., “A 31ns Random Cycle VCAT-based 4F2 DRAM with Enhanced Cell Efficiency,” 2009 Symposium on VLSI Circuits Digest of Technical Papers, pp. 132, 133.